Command-line parameters:

You can use an existent HDL-FSM-Editor project file as last command line parameter.

- Parameter "--no-version-check":

- HDL-FSM-Editor will not access the internet to check for a newer version.

- Parameter "--no-message":

- HDL-FSM-Editor will not print a message at start.

- Parameter "--generate-hdl":

- HDL-FSM-Editor will generate HDL for the given file and exit (batch-mode).

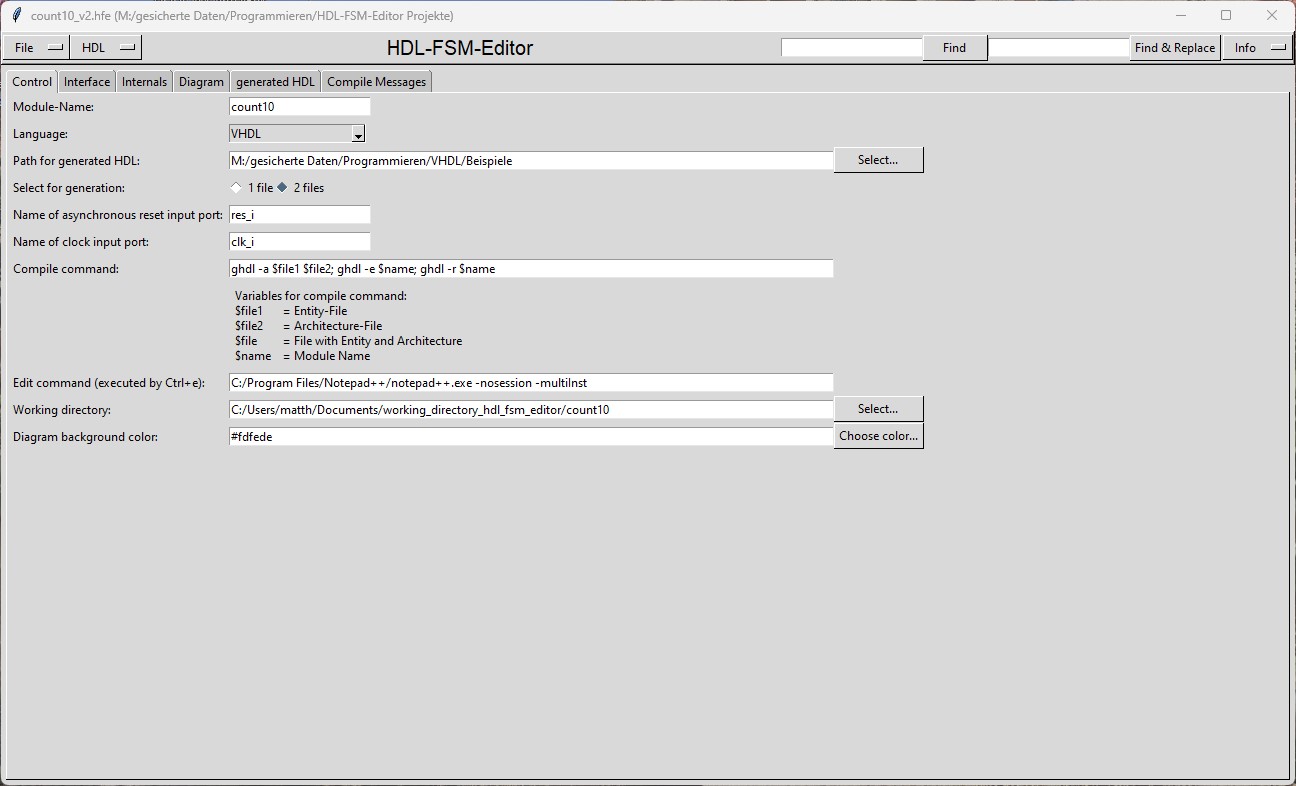

Control-Tab:

Here you define several items which control the generation of the HDL-design, which are:

- Module name:

- Will be used inside the generated HDL and for the filenames of the generated files.

- Language:

- Here you can select between VHDL, Verilog, System-Verilog.

- Path for generated HDL:

- In this folder you will find the generated HDL-files.

- Number of files:

- This is only relevant for VHDL design, where entity and architecture can be stored in different files.

- Name of asynchronous reset input port:

- The signal name specified here will be used as asynchronous reset signal name.

- Name of clock input port:

- The signal name specified here will be used as clock signal name.

- Compile command:

- Here you specify a system command which runs your HDL-compiler/simulator on the generated HDL-code.

- Edit command:

- Here you specify a system command which runs your favoured editor (by Ctrl+e) when editing any text box.

For example:

Windows: notepad++.exe -nosession -multiInst

Linux : gvim -f

- Working directory:

- When the compile commands run they create some files. These files are stored in the working directory.

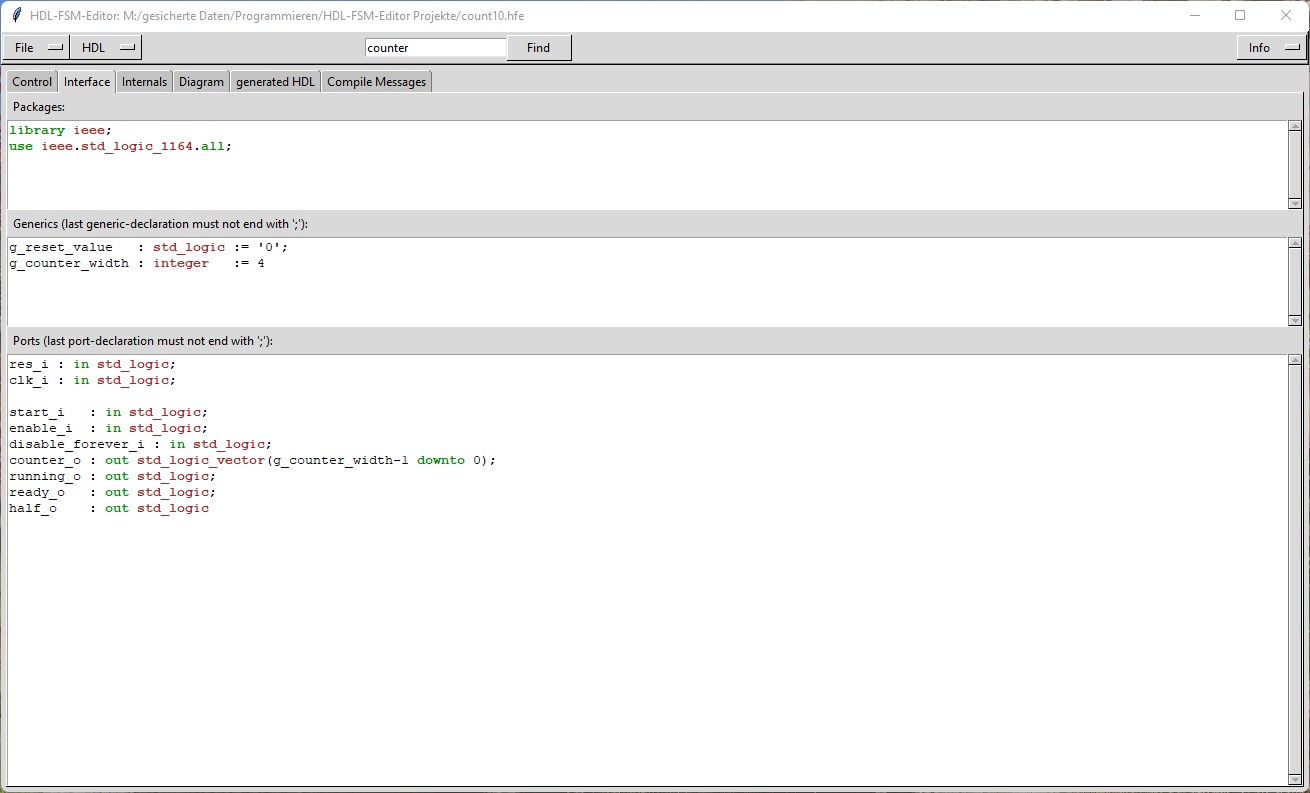

Interface-Tab:

Here you define the interface of your FSM, this means all inputs, outputs, parameters, libraries.

- When you have selected VHDL:

- There is a dedicated text entry field for package-, generic- and port-declarations.

- When you have selected Verilog:

- There is a dedicated text entry field for parameter- and port-declarations.

- When you have selected System-Verilog:

- There is a dedicated text entry field for parameter- and port-declarations.

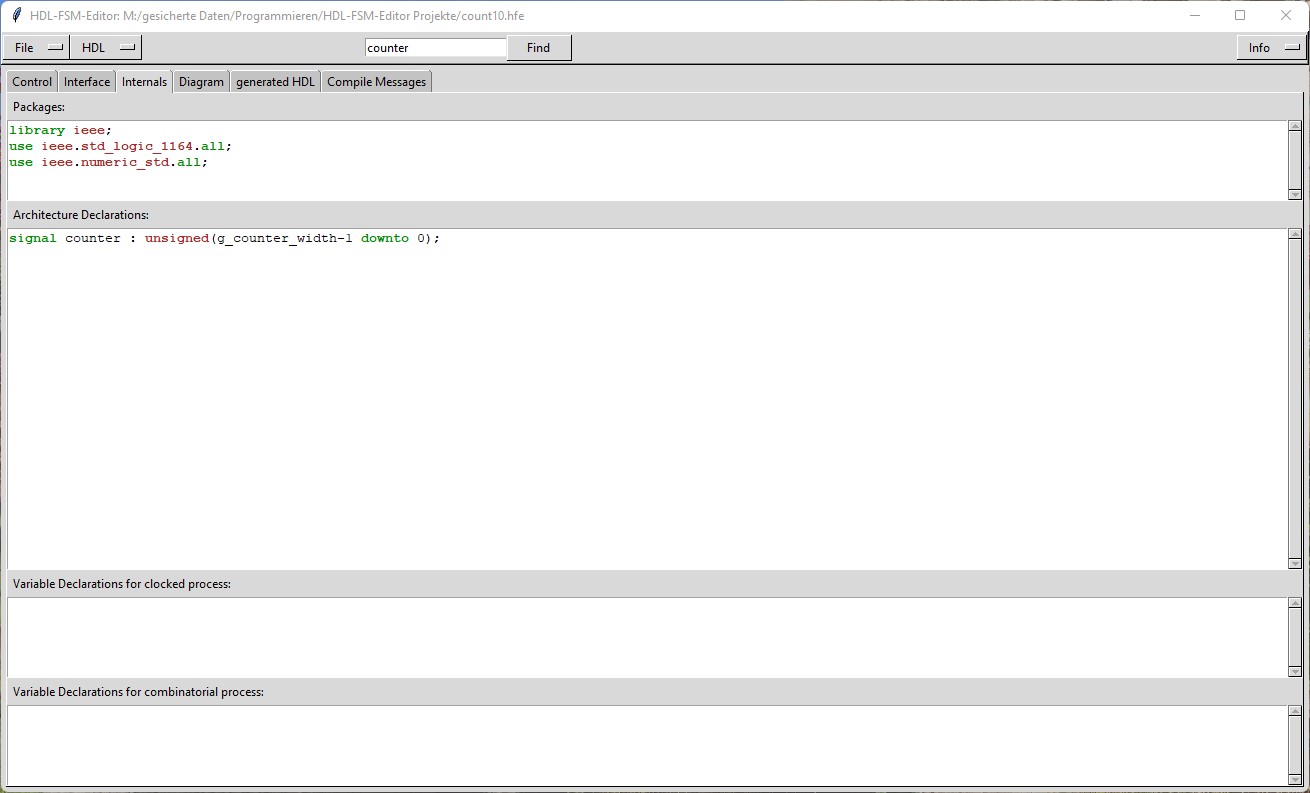

Internals-Tab:

Here you define the internally used signals of your design.

- When you have selected VHDL:

- There is a text entry field for package-, architecture- (like “type”, “signal”),

clocked process variable-, combinatorial process variable- declarations.

- When you have selected Verilog:

- There is a text entry field for internal declarations,

clocked process local variable-, combinatorial process local variable- declarations.

- When you have selected System-Verilog:

- There is a text entry field for internal declarations,

clocked process local variable-, combinatorial process local variable- declarations.

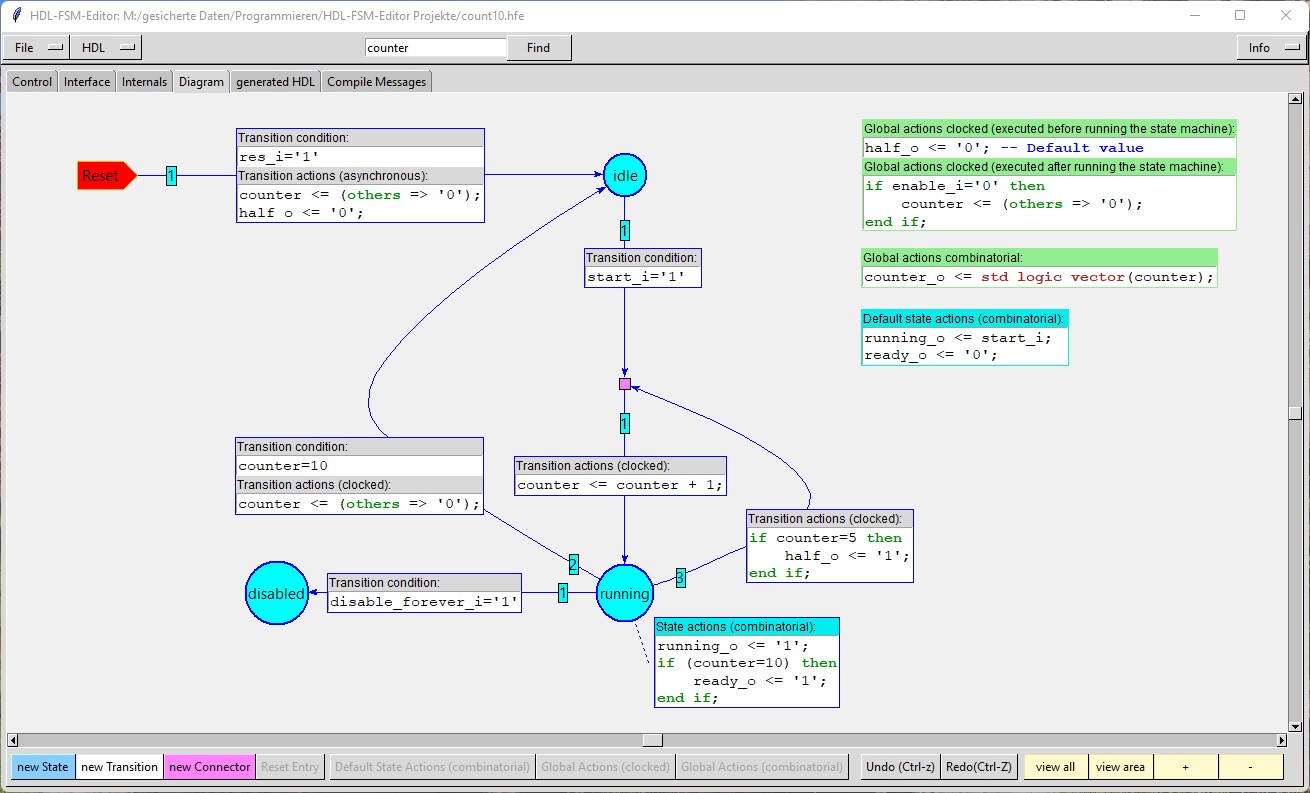

Diagram-Tab:

Here you draw the graphical representation of your FSM.

The following graphical elements are available:

- State:

- You define a state by clicking the “new State” button and placing the state into the diagram.

You can edit the state name by double clicking it, “Return” ends editing, “Escape” aborts editing.

- State-Action:

- Once you have defined a state you can add a state-action for this state by clicking the right mouse button on the state.

Then you get a state-action block where you can define actions which will be executed in a combinatorial way, when the FSM is in that state.

- State-Comment:

- Once you have defined a state you can add a comment for this state by clicking the right mouse button on the state.

Then you get a state-comment block where you can put comments in (without comment characters). The comments will be visible in the generated HDL

- Transition:

- Once you have defined two states you can setup a transition between them by first

clicking the “new Transition” button and

then clicking the start state of the transition and

then clicking at the end state of the transition.

If the FSM is in the start state of the transition, at the next positive clock edge

the FSM will jump into the end state of the transition,

if you do not define any condition for the transition.

When you have implemented several transitions which leave all the same start state, then you must define the transition priority order:

By editing the numbers provided in the transition (double-click), you define the priorities (“Return” ends editing, “Escape” aborts editing).

Priority 1 is the highest priority.

- Condition/Action:

- Once you have defined a transition you can setup a condition and/or an action for that transition by clicking the right mouse button on the transition.

When you have defined a condition, the transition will only fire, if the condition is fulfilled.

If you have defined an action, this action will be executed in a clocked way, when the transition fires.

- Connector:

- You can add a connector by clicking the “new Connector” button and placing it into the diagram.

A connector is used to combine different transitions at their way from start state to end state.

So conditions and actions along each possible path from a start state are executed at a single clock edge.

- Reset Entry:

- You can add exactly 1 reset entry to the diagram by clicking “Reset Entry” and placing it into the diagram.

By connecting the reset entry element with a transition to a state, you define what happens when the reset input signal gets active.

Which polarity of the reset input signal is the active polarity, is defined by the condition of this transition.

In the action block of the transition you define which signals of the design are asynchronously reset to which value.

- Default State Actions:

- As state actions are combinatorial actions (without any storing flipflops),

for each state all combinatorial state action signals must be assigned a value.

This is sometime annoying and can be avoided, by inserting a default state action.

There you define a default value for each state action signal and then you only

need to define a state action,

when a state action signal shall not have its default value.

- Global Actions Clocked:

- Often some clocked logic is needed, which does not depend on the active state of the FSM.

For example, if you assign a default value to a signal in the global action clocked block,

which is executed “before” the state machine, then you must specify in the transition actions

only assignments to the signal, when the signal shall not have the default value.

If you put an action into the global action block, which is executed “after” the state machine,

you can for example “override” the signal changes which are provided by the FSM.

- Global Actions Combinatorial:

- Often some combinatorial logic is needed, which does not depend on the active state of the FSM.

This logic must be put it into this action block.

Hint: As the code of this block is not a part of the FSM, you can enter any legal HDL code.

The following editing actions are available:

- Using the right mouse button you can define a rectangle which defines the visible area in your editor window.

- Using “view area” you can define a rectangle which defines the visible area in your editor window.

- Using “view all” shows the complete diagram in your editor window.

- Using “+” or “-“ zooms in or out. Zooming center is the middle of your editor window.

- Using mouse wheel up or down you can scroll.

- Using “Ctrl” plus mouse wheel (up or down) zooms in or out.

- Using "Ctrl" plus holding the left mouse button, allows moving the visible area.

- Using "Ctrl+e" in a text box loads the text into your editor. After exiting your text editor the edited text is copied into the text box.

- “Undo” and “Redo” buttons are available. You can also use the shortcuts “Ctrl+z” and “Ctrl+Z”.

- A "File" menu for reading and writing files is available (shortcuts are implemented).

- A "HDL" menu for generating HDL and executing the compile-command is available (shortcuts are implemented).

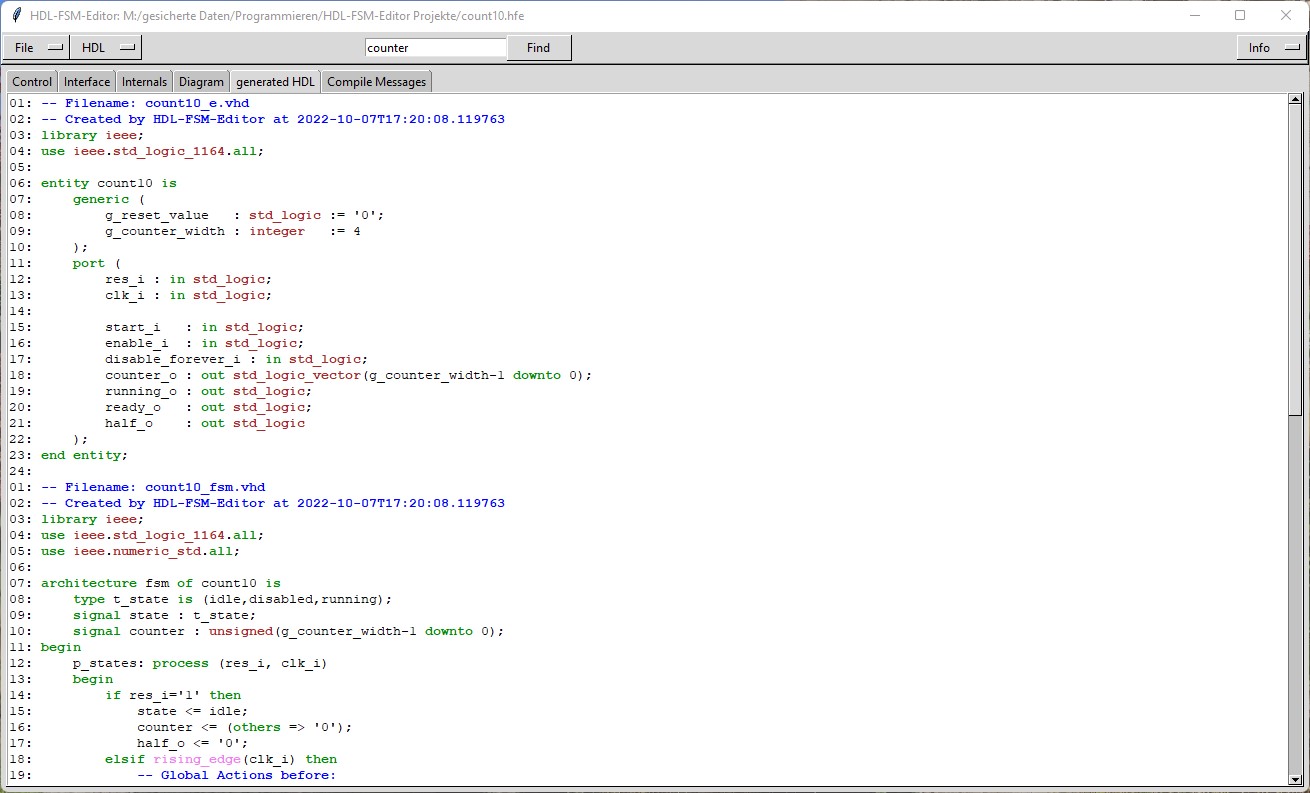

Generated HDL-Tab:

Here the generated HDL files are displayed for reading.

- Each generation replaces the old code with the new code.

- The generated HDL can be loaded into an editor by "Ctrl-e".

- When a code line is linked to the graph in the "Diagram-Tab", then the code line will be underlined, when the mouse pointer is at it.

- To follow the link the user must press the left mouse button together with the Ctrl-key.

- The diagram element which represents the code line will then be shown and highlighted.

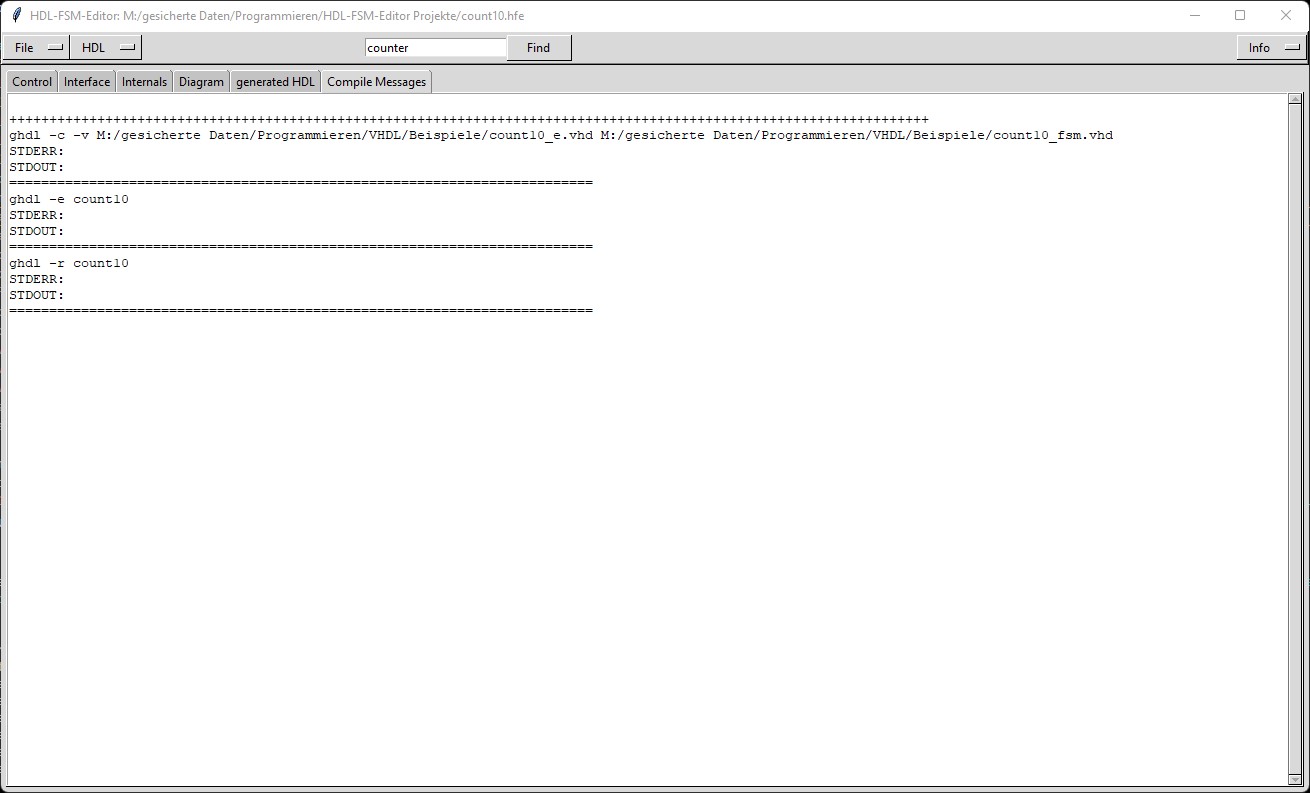

Compile Messages Tab:

The STDOUT and STDERR messages of the compile command appear in this tab.

- The tab is only cleared at a new start of HDL-FSM-Editor, or when you switch to a new design (using “open” or “new”).

- The messages can be loaded into an editor by "Ctrl-e".

- When a line is linked to the "Generated HDL-Tab" and to the graph in the "Diagram-Tab", the line will be underlined, when the mouse pointer is at it.

- To follow the link to the "Diagram-Tab" the user must press the left mouse button together with the Ctrl-key.

- To follow the link to the "Generated HDL"-tab the user must press the left mouse button together with the Alt-key.

- Per default the links are based on the message format of the "GHDL" VHDL-Compiler or the "iverilog" Verilog-Compiler.

- The message format can be adapted by using the Button "Define Regex for Hyperlinks".

Adapting the regular expression for the links:

- Per default the links for VHDL are based on the messages of the GHDL-VHDL-Compiler which look like: "M:/test.vhd:59:5: < some error message >" .

- Per default the links for Verilog are based on the messages of the iverilog-VHDL-Compiler which look like: "M:/test.v:59: < some error message >" .

- For following the link, the file-name and the line-number must be extracted from this message.

- This is done by a regular expression which encloses the complete line and defines 2 groups.

- One group contains the file-name, the other group contains the linenumber.

- Then, to get the file-name, the complete line is replaced by the group which contains the file-name.

- Then, to get the line-number, the complete line is replaced by the group which contains the line-number.

- In order to adapt the regular expression to another HDL compiler the button "Define Regex for Hyperlinks" must be pressed.

- Then a dialog pops up, where the regular expression for the complete line and the 2 groups can be entered.

- In the 2 additional fields the group for the file-name and the group for the line-number must be specified.

- For the test of a different regular expression please use https://regex101.com.

- A debug mode for the regular expression can be activated, which gives information at STDOUT.

License:

HDL-FSM-Editor

Copyright (c) 2024 Matthias Schweikart

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"),

to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense,

and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED,

INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT.

IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Files:

Python3 source code:

(Start the tool by "python3 main.py" or

create an executable with 'pyinstaller --onefile --icon rsc/hfe_icon.ico --add-data "rsc/hfe_icon.ico;rsc" -n hdl_fsm_editor src/main.py')

Executable for Windows 11:

Executable for Linux (compiled with Linux-Mint):

Small example project:

Change log:

Version 5.9 (07.12.2025):

- Deleting an object in the diagram did sometimes not work or did delete the wrong object. Fixed.

- At storing in a file sometimes an exception happened (caused by rounding of coordinates.). Fixed.

- Some refactoring.

Version 5.8 (01.12.2025):

- Scrolling and zooming does no longer modify the data written to the hfe-file.

- At Linux Mint at leaving a condition&action window, the condition&action block was not shrinked anymore. Fixed.

- At slow Linux Mint systems the condition&action block, and all other block types too, jumped at moving. Fixed.

- The entry boxes of the Control-tab expand now together with the window.

- The radio button for the number of files has been moved from the right-hand border to the middle.

- Highlighting when VHDL attributes are used is improved.

- Refactoring: Find&Replace is now moved in its own class.

- Find&Replace now works also in the Control-tab.

- VHDL-function calls are not highlighted red anymore.

- Refactoring of linting.py.

Version 5.7 (28.10.2025):

- Delete state and delete state-action did not work since version 5.5. Fixed.

- Signal names containing the string "end_" where sometimes highlighted in a wrong way. Fixed.

- After changing an text by an external editor and saving the design, leaving a block with the mouse pointer signaled "design has changed". Fixed.

- Linting highlighted 'x' of x"12AB" in red. Fixed.

- Change detection in "global actions combinatorial" signaled design change too often. Fixed

- In batch mode the warning about a wrong state order is now printed at STDOUT and not in a pop up dialog.

- In batch mode warnings during file read are now printed at STDOUT instead in pop up dialogs.

- In batch mode the warning about a wrong state order is now printed at STDOUT and not in a pop up dialog.

- Linting can now handle VHDL procedures.

- A start from command line only with file-parameter does not activate script-mode anymore.

- Added linting for user defined processes in "Global Actions Combinatorial".

- At reading from a hfe-file now a existing ".tmp" file is always removed.

- The timestamp checkbox was moved into the "Select for generation" line.

Version 5.6 (17.10.2025):

- At reading a design sometimes an exception regarding variable "trans_id" happened. Fixed.

- When a curved transition is moved, sometimes the transition shape gets strange at pick up. Fixed.

- The cursor now changes shape during file operations to signal to the user that they must wait.

- Removed second implementation of priority box drawing from undo_handling.

- A warning pop up dialog informs the user, when a state is placed too near to another object.

- Improved robustness when moving transitions (avoiding null vectors).

- When the "generated HDL" was opened sometimes no HDL was loaded. Fixed.

- Some refactoring.

Version 5.5 (04.10.2025):

- Inserting a new transition activated the message box "corrupt database" with no reason. Fixed.

- A senseless attempt to remove the line to a state-action/comment box caused an exception. Fixed.

- After an Undo operation the new move method did not work for states anymore. Fixed.

- The end point of a connection line of a state action/comment jumped sometimes to the grid. Fixed.

- The state menu can now also be opened over a state name.

- Removed useless highlighting at entering a line to a state-action/comment box.

- Removed unused parameter move_to_grid of method move_to for canvas-windows.

- Removed second implementation of transition drawing from file_handling.

- Removed second implementation of priority box drawing from file_handling.

Version 5.4 (02.10.2025):

- Fix for new move method.

- Support of reading HFE Version 1 files was removed.

- State-Insertion at reading from a file now uses the state-insertion-methods from the user interface instead of own ones.

Version 5.3 (02.10.2025):

- Picking up objects for moving was sometimes kind of hard. Fixed.

- Moving the cursor into any action or comment block (without any code change) could set the design state to "modified". Fixed.

- Names containing the string "warning" or "error" were highlighted red in the "Compile Message" tab. Fixed.

- Sometimes states may be shrinked during moving. Fixed.

- Added a title for the "select HDL directory" dialog.

Version 5.2 (16.08.2025):

- Creating HDL in batch mode did not work because of an exception. Fixed.

- Refactoring to reduce the number of linter warnings.

Version 5.1 (04.08.2025):

- Added the "Additional sources" entry field to the Control-tab. Will be used only by HDL-SCHEM-Editor.

- The STDOUT messages at startup are now copied into the "Compile messages" tab.

- Linting (highlighting of never read or never written signals) now can handle VHDL-records.

- When a Condition&Action box was entered, sometimes the box switched permanently between its small and big size. Fixed.

- When the HDL-tab was updated, sometimes the old HDL was not removed. Fixed.

Version 5.0 (01.08.2025):

This update introduces improvements to the HDL-FSM-Editor, including new features, refactoring, enhanced testing, and documentation updates. Key highlights include:

- Comprehensive test suite with parallel execution support

- Application icon

- Type annotations, linting, and formatting

- Documentation with a new CHANGELOG.md and updated README.md at Github

- Changed unsaved changes dialog

- Added hdl-generation without timestamp feature

- When executed in batch-mode there is now a return code

- Changed and improved the regex-dialog

- Restructure the application source code layout

- Github release script to build and release the application

- Enhanced .vscode integration

Version 4.12 (20.07.2025):

- If the first line of a state comment only contains an integer, this value will determine the order of the states in the generated HDL.

- Using shortcuts with captitalised characters now creates a warning message.

- In VHDL 2-files mode now not only the entity-file is checked for updates (caused by another instance of HFE) but also the architecture-file.

- When inserting a transition was aborted by "Escape", then moving the state where the transition started, caused an exception. Fixed.

- "Undo" after deleting a textbox (like "Global Actions") created sometimes graphical artefacts. Fixed.

- The "New" button cleared the canvas but did not activate the grid. Fixed.

- Since version 4.11 the Verilog in the generated-HDL tab was completely colored as comment. Fixed.

- Control-s and Control-g inside any modified text box saved the design, but moving the cursor outside the box,

did set the status of the design back to "modified". Fixed.

Version 4.11 (27.03.2025):

- The solution for moving textboxes by picking them inside (not at the border) introduced in Version 3.8 showed

poor graphical behaviour under Linux Mint (boxes hopping around uncontrollable).

This solution also prevented text selecting by the mouse inside the box, because the box was moved instead.

Therefore a new solution was implemented, which behaves well under Linux and allows selecting text again.

The new solution highlights the border of the box, when the mousepointer has reached a position,

which allows to move the box.

- The sensitivity list of the state-action-process sometimes was incomplete. Fixed.

- If a state had a comment, it could not be renamed. Fixed.

- If a state had a comment and was deleted, the comment remained as a relic and had to be deleted separately. Fixed.

- A VHDL block comment in a port or generic list prevents correct linting-highlighting on the following identifier. Fixed.

- A condition or action which contained only a '.' caused an infinite loop at syntax highlighting. Fixed.

- When HDL-SCHEM-Editor starts HDL-FSM-Editor for HDL generation under Linux, the message "There are unsaved changes.." popped up without any reason. Fixed.

- At opening a new design the new design was marked with '*' as changed. Fixed.

- If a state name has been modified into a significantly longer one and outgoing transitions had a priority rectangle,

then the new statename was sometimes not accepted. Fixed.

- At deleting a transition a wrong tag-plausibility warning was sometimes raised. Fixed.

- Editing transition priorities did not work after an Undo. Fixed.

- Now at HDL generation it is checked if a transition is hidden, because a transition with higher priority has no condition.

- VHDL block comments are now highlighted blue.

- A search for an empty string is now rejected with a message.

- Regular expressions in search- or replace-string are now always ignored.

- When the "generated HDL" tab is opened, it is now checked if newer HDL is available at disk.

Version 4.10 (25.02.2025):

- A bug prevented the new backup function from working. Fixed.

- Syntax highlighting did not work correctly, when functions were declared in the "Internals"-tab. Fixed.

- Syntax highlighting did not work correctly, when '+' or '-' characters were not surrounded by blanks. Fixed.

- Again sometimes the sash positions in Interface/Internals-tab made the text fields unvisible. Fixed.

- The VHDL type definition for the state signal now is broken into several lines, when more than 10 states exist.

Version 4.9 (21.02.2025):

- HDL-FSM-Editor now creates a backup file during editing, where all changes are stored and from

which the design can be automatically recovered after a crash.

- The states are now a little bit bigger to avoid overlapping of state name and state circle.

- A double click at a word now does not select the following ';' or ','.

- The "compile through hierarchy" command now inserts a "Finished"-line into the message tab.

- The values "true" and "false" were highlighted red as a "not written signal". Fixed.

- Highlighting of signal names did not work correctly if VHDL attributes were used. Fixed.

- Highlighting of signal names sometimes did not work correctly after find&replace. Fixed.

- Added missing VHDL keywords for syntax highlighting.

- Since version 4.5 sometimes the messages in the messages tab were highlighted in the wrong color. Fixed.

- When HDL-SCHEM-Editor opened a HDL-FSM-Editor VHDL design, "library ieee;..." was added each time to the Interface-tab. Fixed.

Version 4.8 (12.02.2025):

- There was a bug in HDL generation which caused missing transition actions in HDL.

The problem showed only at complicated structures of transitions and connectors between 3 (or more) states. Fixed.

- The grid lines are not written in the hfe-file anymore.

- The grid lines were not shown by the command "view area". Fixed.

- The grid lines were not redrawn after a shift by Control-Button-1. Fixed.

- "view all" sometimes did not use the full canvas area. Fixed.

- The moving of curved transitions with 3 or 4 points now works better.

- The highlighting of signal names did not always work as expected during find&replace. Fixed.

- The tag plausibility is now not only checked at HDL generation but also at file write.

- Sometimes a priority rectangle was shown when only 1 transition leaves a connector. Fixed.

- Sometimes the sash positions in Interface/Internals-tab made the text fields unvisible. Fixed.

- When the size of a state was changed, the connected transitions were shown dashed afterwards if the grid was visible. Fixed.

- During syntax highlighting no "bold" characters are used anymore, in order to prevent the text

from getting shifted out of its textbox (lines with bold characters are higher).

Version 4.7 (05.02.2025):

- After start of HDL-FSM-Editor per command line with file-parameter the opened design was not shown in "view all" view. Fixed.

- At start of HDL-FSM-Editor per command line with file-parameter now the filename-extension is checked (must be .hfe).

- An undo of a Find&Replace-Action now also un-does changes in Interface- and Internals-Tab.

- Short-cuts for Undo/Redo are now shown at top of the text-widgets in Interface- and Internals-Tab.

- If actual HDL was found to copy into "generated HDL"-tab at loading a design, then new generated

HDL (identical to the actual one besides the time-stamp) was written into the "generated HDL"-tab. Fixed.

- Generated HDL now includes only a comment with its file-name and not with its complete path-name anymore.

- The Undo/Redo buttons in the "Diagram"-tab are now enabled/disabled depending on the content of the undo stack.

- Now the Find&Replace is able to replace a string by an empty string.

- The error message for a not existing folder for the generated HDL was changed to get more information.

Version 4.6 (18.12.2024):

- The batch HDL-generation (hdl_fsm_editor -generate_hdl file.hfe, used by HDL-SCHEM-Editor) did crash for some designs. Fixed.

Version 4.5 (16.12.2024):

- A grid is now displayed in the "Diagram"-tab after start up.

- The grid can be hidden by the right mouse button menu in the "Diagram"-tab.

- The background color of the "Diagram"-tab can now also be changed by the right mouse button menu in the "Diagram"-tab.

- The size of the entry windows in the "Interface" and "Internals"-tab can now be adapted by moving the separating bars.

- The size of the entry windows in the "Interface" and "Internals"-tab is now stored in the saved file.

- The search per "Find"-button now also searches in state-comments.

- There is now a "Find & Replace" button available.

- After "Find" or "Find & Replace" now the number of hits/replacements is displayed.

- In the "Compile Messages"-tab now STD_ERR and STD_OUT are not separated anymore.

- In the "Compile Messages"-tab now warnings and errors are colored red.

- In the "Compile Messages"-tab now VHDL report message are displayed green.

- The "Compile Messages"-tab now has a "Clear"-button.

- When HDL generation is started and not saved changes exist, then first the design is automatically saved.

- When HDL-FSM-Editor is started, then the IEEE.std_logic_1164-package is automatically added in the "Interface"-tab.

- Sometimes the arrowhead of a transition was not displayed. This caused also an exception when the transition was reshaped. Fixed.

- A left mouse button click during view-area with the right mouse button caused an exception. Fixed.

- After loading a design from file, connectors did not get highlighted when the mouse pointer entered. Fixed.

- Moving connectors by mouse pointer now works better when the connector is very small.

- Picking up a state for moving now works better when the state is very small.

- Now the transition priority rectangle gets also invisible, when the number of outgoing transitions is reduced to 1 by deleting another state.

Version 4.4 (02.10.2024):

- The background color of the diagram can now be configured in the control tab.

- The color of a state can now be configured by using the right mouse button menu at the state.

- Since version 4.3 a state-name could no longer be changed to the name it had already. Fixed.

- When transition end points were moved from one state to another state, the priority rectangles were not shown or hidden accordingly. Fixed.

- Now also the priority rectangle of the transition from the reset-entry is hidden.

- States and Connectors can no longer be placed on top of each other (caused exceptions sometimes).

- When a design is opened always the diagram is shown, even if HDL is loaded into the "generated HDL" tab.

- A transition which starts at reset entry can no longer be ended at a connector.

- A start-point of a transition can no longer be moved to the reset-entry if there already another transition starts.

Version 4.3 (30.09.2024):

- Inserting a transition can now be aborted by "Escape".

- When a transition had the shape of the letter 'S', then only the end points of the transition could be moved by the mouse pointer. Fixed.

- There is the new menu entry "straighten shape" at the right mouse button menu of a transition which changes the shape of transition to a straight line.

- The priority boxes of outgoing transitions of a state are only shown if the state has more than 1 outgoing transition.

- When a transition is inserted, its priority is automatically set to the highest unused priority

- When a state-name is changed, it is now checked if the new state-name is already used.

- Generics/parameters- and ports-declaration lists are now allowed to have a list separator (;/,) even after the last entry of the list.

- When a hfe-file is read by HDL-FSM-Editor and the generated HDL is younger than the hfe-file, then the generated HDL is copied into the HDL-tab.

- Unread or unwritten signalnames were highlighted red in state comment blocks. Fixed.

Version 4.2 (05.09.2024):

- Adding comments to states in a comment-box is now supported.

- Sometimes the plausibility checks report unnecessarily an unknown tag named "current", which is a legal tag and must be ignored. Fixed.

- Sometimes comments in transition-conditions caused illegal HDL code. Fixed.

- After inserting the reset-entry it is not longer necessary to abort the reset-entry-insertion by Escape.

Version 4.1 (27.08.2024):

- At HDL generation the database is checked for plausibility.

If any error is found an error-message is shown and the errors are listed at STDOUT.

Errors could be introduced by program malfunction or by editing manually the hfe-file.

- When a condition-action window was removed, sometimes the connection-line of the window was not removed from the database. Fixed.

- When a connector box had no leaving transition and HDL was generated a Python exception happened. Fixed.

Version 4.0 (14.06.2024):

- Now Links from the HDL-code in the "generated HDL"-tab to the source in the "Diagram"-tab are supported.

- Now Links from the compiler messages in the "Compile Messages"-tab to the "generated HDL"-tab or the source in the "Diagram"-tab are supported.

- Local Variable Declarations for clocked always process were added to the HDL code in a wrong way. Fixed.

- Improved HDL formating when transition conditions are more than 1 line of code.

Version 3.11 (05.05.2024):

- In VHDL-mode the sensitivity list of the p_state_action process sometimes had duplicate entries. Fixed.

- In Verilog-mode the declaration of an integer variable caused an error message at HDL generation. Fixed.

- In Verilog-mode the linting (giving colors to not read or not written signal names) did not always use correct colors. Fixed.

- In Verilog-mode now reg/wire/logic can be declared as "signed" or "unsigned".

- The window title now has another format, so that the design name can be read, when the window is an icon.

Version 3.10 (13.03.2024):

- Loading a design into HDL-FSM-Editor by command line parameter did not work anymore in version 3.9. Fixed.

- Fixed wrong tool-name in the help-text shown by option "-h".

- Added new command-line parameter "-generate_hdl" for batch-mode HDL generation (used in HDL-SCHEM-Editor).

Version 3.9 (07.03.2024):

- The window-title was changed, so that the filename can be read, if the window is an icon.

- The checking of the command line parameters is now done by ArgParse.

- The new command-line switch -no_message was introduced to prevent HDL-FSM-Editor to print a message at start.

Version 3.8 (23.11.2023):

- Now also the Default State Action block can be moved by picking it inside.

- A working directory for the compile commands can now be specified in the control tab.

Version 3.7 (17.11.2023):

- All action blocks could only be moved by touching them near there border. Now they can be touched also inside.

- Connectors were not inserted with the right size after a zoom. Fixed.

Version 3.6 (08.11.2023):

- Using the "Edit command" (Control-e) under Linux did not work. Fixed.

Version 3.5 (23.10.2023):

- At HDL generation correctly defined functions and types caused the warning "There is an illegal signal declaration". Fixed.

- When a generic is read by an assignment it was colored red, as it was never written. Fixed.

Version 3.4 (21.10.2023):

- At HDL generation correctly defined HDL-constants caused the warning "There is an illegal signal declaration". Fixed.

- Constants were highlighted in red as "not written". Fixed.There is an illegal signal declaration

Version 3.3 (18.09.2023):

- Added command line switch "-no_version_check" to forbid HDL-FSM-Editor to access the internet at start.

- Removed a HDL generation crash, which was caused by a transition with no condition using a connector.

Version 3.2 (20.06.2023):

- Fixed uncritical key error (caused only error messages at StdOut) when using the Internals/Packages entry window. Error was introduced in version 2.0

Version 3.1 (19.06.2023):

- In HDL all actions of a transition from a start state to a target state were implemented in the last condition branch of the transition. Now actions which may not have to be executed in this last branch are "moved up" in the branch hierarchy, which leads to shorter and better readable code.

Version 3.0 (30.05.2023):

- A new algorithm for transforming the transition conditions and actions into HDL is now implemented. The old algorithm caused problems when connectors were used excessively.

- HDL-FSM-Editor now gives a hint, when a newer version is available.

Version 2.1 (12.05.2023):

- A Verilog wire declaration added in "Internal Declarations" will not cause an (unimportant) Error message anymore.

Version 2.0 (04.05.2023):

- Now the JSON format is used when a design is saved to a file. The file menu has a new entry for reading the old format of Version 1.

- "view area" can now be also done by the right mouse button.

- When a new design is opened by open-file dialog, the old design is not not removed, when the user aborts the opening.

- When selecting the path for the generated HDL, an abort does not remove the old path entry anymore.

- Now also in any Interface/Internals text field Control-o opens a file-dialog, instead of inserting a new line.

- Fixed loading a design by a command line with "hdl_fsm_editor design-file.hfe". This did not work since version 1.4.

- Deleting empty condition&action- and state-action- windows now works.

- After inserting Default-State-Actions, Global-Actions and Global Actions-Combinatorial the escape key must not be pressed anymore.

Version 1.9 (09.01.2023):

- The error message, which occurs when the reset condition is missing, now gives the user a hint, where the reset condition must be specified.

Version 1.8 (07.01.2023):

- In Verilog-mode now the temporay file (which is created when ctrl+e is used in a textbox) has the extension ".v" instead of ".vhd".

- The time stamp format used in generated HDL and in the "Compile Messages" tab is now better readable.

Version 1.7 (21.12.2022):

- Fixed: main_window.py from version 1.6 had a doubled "," in line 266 instead of a single one.

Version 1.6 (09.12.2022):

- Fixed a bug which showed, when a VHDL port name contains the string "out".

- For text fields now no default font is used anymore (keywords and non-keywords now always use the same font).

Version 1.5 (08.11.2022):

- A change of the path for the generated HDL is now handled as a design change.

- A bug at moving transitions was fixed.

- The print functionality was removed, as each action window is always printed as a black box.

Version 1.4 (25.10.2022):

- Several small bugs were fixed.

- Static code analysis was added: Not read signals appear in "orange", not written signals appear in "red".

Version 1.3 (10.10.2022):

- Bug at highlighting was fixed.

- Find-Button was added.

- When editing text boxes an external editor can be started by Control-e.

- Improvements for moving items in the diagram tab were added.

Version 1.2 (04.10.2022):

- SystemVerilog is now supported.

- Keyword highlighting is supported.

- Verilog: Asynchronous reset is now correct implemented.

Version 1.1 (29.09.2022):

- Verilog is now supported.

- VHDL or Verilog code using upper case characters is now handled correctly.

- When deleting windows from the state diagram, it is now easier to hit the target.

- HDL-Generation: 1 file mode now works.

Version 1.0 (25.09.2022):